# Intel<sup>®</sup> 7 Series Family-Intel<sup>®</sup> Management Engine Firmware 8.1

## 1.5MB Firmware Bring Up Guide

July 2012

Revision 8.1.0.1248 - PV Release

Intel Confidential

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

All products, platforms, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice. All dates specified are target dates, are provided for planning purposes only and are subject to change.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

Intel® Active Management Technology requires activation and a system with a corporate network connection, an Intel® AMT-enabled chipset, network hardware and software. For notebooks, Intel® AMT may be unavailable or limited over a host OS-based VPN, when connecting wirelessly, on battery power, sleeping, hibernating or powered off. Results dependent upon hardware, setup & configuration. For more information, visit <a href="https://www.intel.com/technology/platform-technology/intel-amt">https://www.intel.com/technology/platform-technology/intel-amt</a>.

No system can provide absolute security under all conditions. Requires an enabled chipset, BIOS, firmware and software, and a subscription with a capable Service Provider. Consult your system manufacturer and Service Provider for availability and functionality. Intel assumes no liability for lost or stolen data and/or systems or any other damages resulting thereof. For more information, visit <a href="https://www.intel.com/go/anti-theft">https://www.intel.com/go/anti-theft</a>.

KVM Remote Control (Keyboard, Video, Mouse) is only available with Intel<sup>®</sup> I Core™ i5 vPro and Core™ i7 vPro processors with Intel<sup>®</sup> Active Management technology activated and configured and with integrated graphics active. Discrete graphics are not supported.

Systems using Client Initiated Remote Access require wired LAN connectivity and may not be available in public hot spots or "click to accept" locations.

Warning: Altering clock frequency and/or voltage may (i) reduce system stability and useful life of the system and processor; (ii) cause the processor and other system components to fail; (iii) cause reductions in system performance; (iv) cause additional heat or other damage; and (v) affect system data integrity. Intel has not tested, and does not warranty, the operation of the processor beyond its specifications.

Code names featured are used internally within Intel to identify products that are in development and not yet publicly announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user.

Intel, Intel® vPro™, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2012, Intel Corporation. All rights reserved.

# **Table of Contents**

| 1   | Introduction                                                       | 8  |

|-----|--------------------------------------------------------------------|----|

| 1.1 | Related Documentation                                              | 8  |

| 1.2 | Intel® ME FW Features                                              | 8  |

| 1.3 | Prerequisites                                                      | 9  |

| 1.4 | Acronyms and Definitions                                           | 9  |

|     | 1.4.1 General                                                      | 9  |

|     | 1.4.2 Intel <sup>®</sup> Management Engine                         |    |

|     | 1.4.3 System States and Power Management                           | 11 |

| 1.5 | Reference Documents                                                | 12 |

| 1.6 | Format and Notation                                                |    |

| 1.7 | Kit Contents                                                       |    |

| 1.8 | External Hardware Requirements for Bring Up                        | 16 |

| 2   | Image Creation: Flash Image Tool (FITC)                            |    |

| 2.1 | Start FITC and Set Up The Build Environment                        |    |

| 2.2 | Configure PCH Silicon Stepping                                     |    |

| 2.3 | Set Up SPI Flash Regions                                           |    |

| 2.4 | Set Up Descriptor and SPI Flash Device(s)                          |    |

|     | 2.4.1 Set Up Soft-Straps                                           |    |

| 2.5 | Configure PCH Silicon SKU                                          |    |

| 2.6 | Intel®ME FW Feature Configuration                                  |    |

|     | 2.6.1 Firmware Features and Capabilities                           |    |

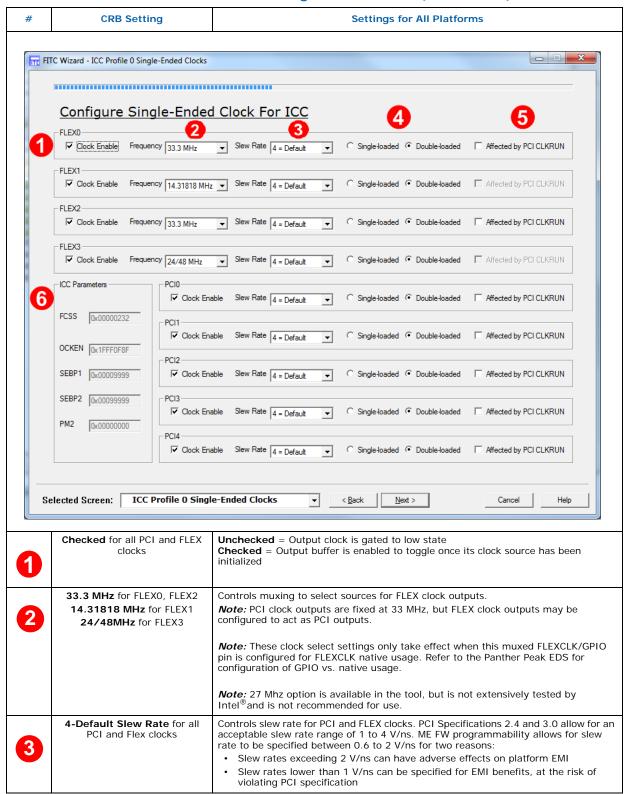

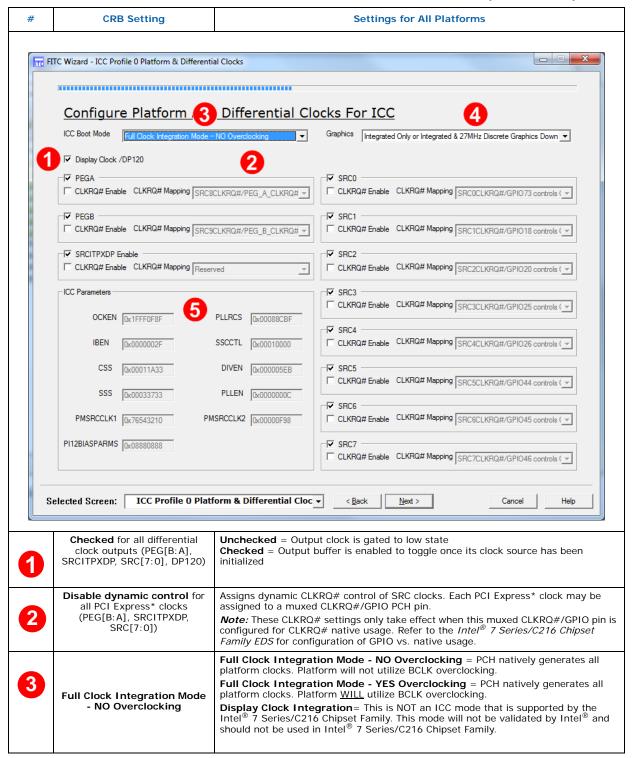

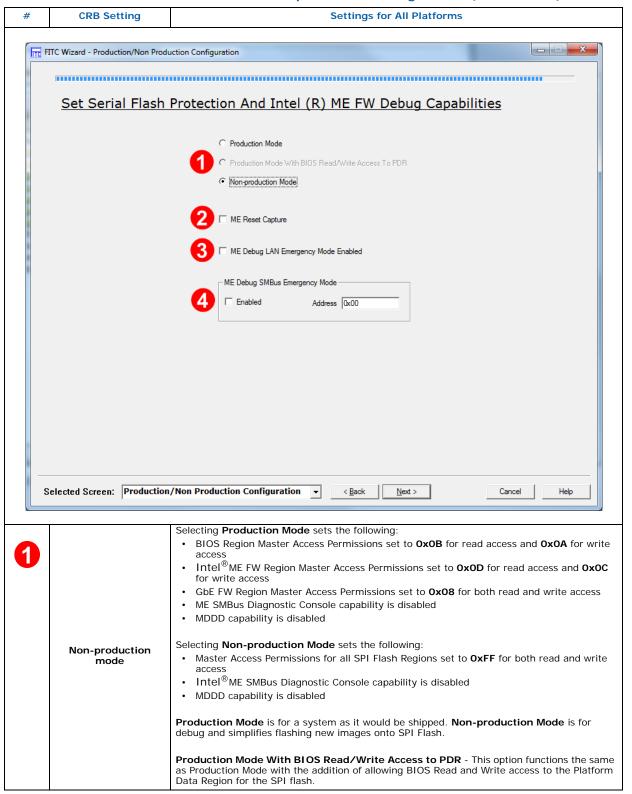

|     | 2.6.2 Clock Control Parameters                                     |    |

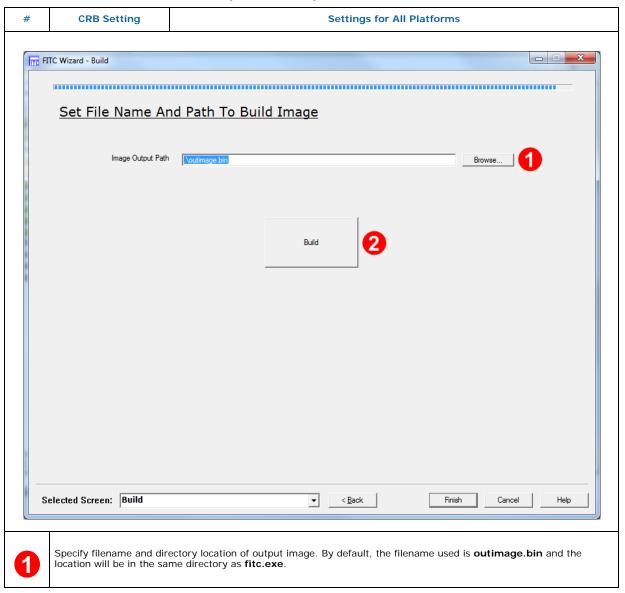

| 2.7 | Build SPI Flash Binary Image                                       |    |

|     | 2.7.1 Build SPI Flash Binary Image                                 |    |

|     | 2.7.2 Save Your Settings                                           |    |

|     | 2.7.3 Protect Saved Configuration XML File                         | 50 |

| 3   | Programming SPI Flash Devices and Checking Firmware Status         | 53 |

| 3.1 | Flash Burner/Programmer                                            | 53 |

| 3.2 | Flash Programming Tool (FPT)                                       | 53 |

|     | 3.2.1 FPT Windows* Version                                         | 54 |

| 3.3 | Checking Intel <sup>®</sup> ME Firmware Status                     | 55 |

| 3.4 | Common Bring Up Issues and Troubleshooting Table                   | 57 |

| Α   | Appendix — Flash Configurations                                    | 59 |

| В   | Appendix — Intel® C600 Series Express Chipsets Clock Configuration | 61 |

| B.1 | Functional Blocks                                                  |    |

| B.2 | Clock Configuration XML                                            |    |

| B.3 | Intel®ME FW Clock Control Parameters                               | 63 |

|     | B.3.1 CSS – Clock Source Select                                    | 63 |

|     | B.3.2 SSS – SRC Source Select                                      |    |

|     | B.3.3 FCSS – Flex Clock Source Select                              | 65 |

| B.3.4  | PLLRCS – PLL Reference Clock Select                          | 69 |

|--------|--------------------------------------------------------------|----|

| B.3.5  | DPLLAC – Display PLL "A" Configuration                       | 70 |

| B.3.6  | DPLLBC – Display PLL "B" Configuration                       | 70 |

| B.3.7  | PLLEN – PLL Enable                                           | 70 |

| B.3.8  | OCKEN – Output Clock Enable                                  | 70 |

| B.3.9  | IBEN – Input Buffer Enable                                   | 72 |

| B.3.10 | DIVEN – Divider Enable                                       | 73 |

| B.3.11 | PM1 – Power Management                                       | 74 |

|        | PM2 – Power Management                                       |    |

| B.3.13 | SEBP1 – Single Ended Buffer Parameters                       | 75 |

| B.3.14 | SEBP2 – Single Ended Buffer Parameters                       | 76 |

| B.3.15 | SSCCTL – SSC Control                                         | 78 |

| B.3.16 | PMSRCCLK1 – SRC Power Management                             | 79 |

| B.3.17 | PMSRCCLK2 – SRC Power Management                             | 81 |

|        | PI12BiasParms – Phase Interpolators 1 & 2 Biasing Parameters |    |

|        | SSC2OCPARMS – SSC2 Overclock Parameters                      |    |

|        | PCH Clock output / ICC registers mapping - part A            |    |

| B.3.21 | PCH Clock output / ICC registers mapping - part B            | 86 |

## **Figures**

| 2-1<br>2-2   | Build   Environment Variables                                                          |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------|--|--|--|--|

| 2-3          | PCH Silicon Stepping Combo Box                                                         |  |  |  |  |

| 2-4          | <u> </u>                                                                               |  |  |  |  |

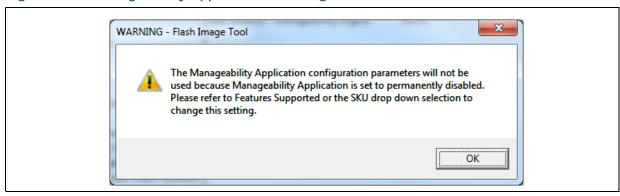

| 2-5          | Manageability Application Warning                                                      |  |  |  |  |

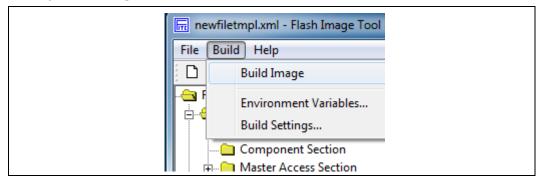

| 2-6          | Build   Build Image 5                                                                  |  |  |  |  |

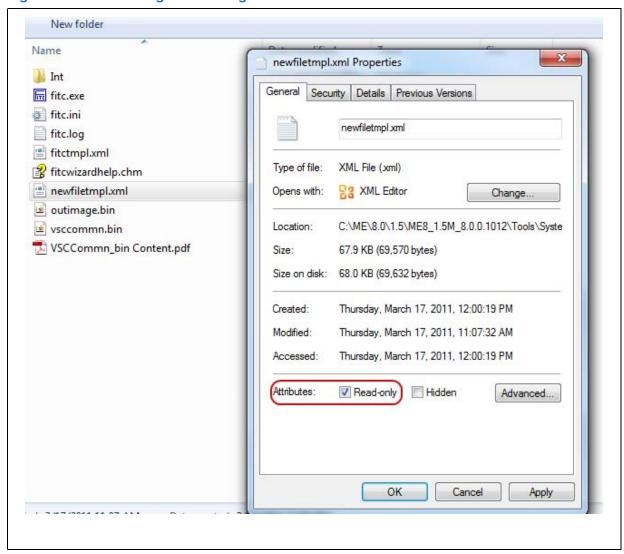

| 2-7          | Protecting FITC Configuration XML File                                                 |  |  |  |  |

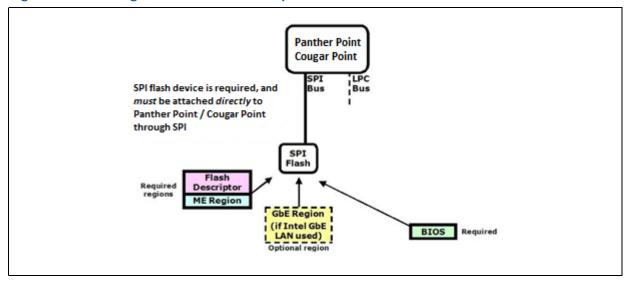

| A-1          | Configuration "A" — Desktop/Server/Workstation or Mobile                               |  |  |  |  |

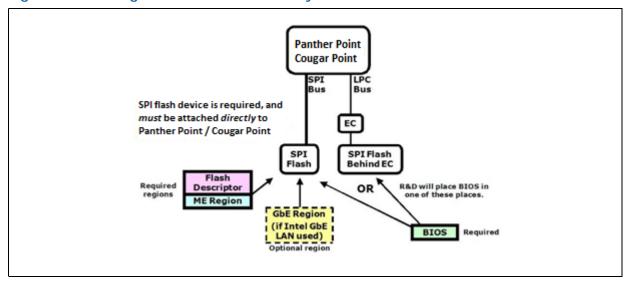

| A-2          | Configuration "B" — Mobile Only                                                        |  |  |  |  |

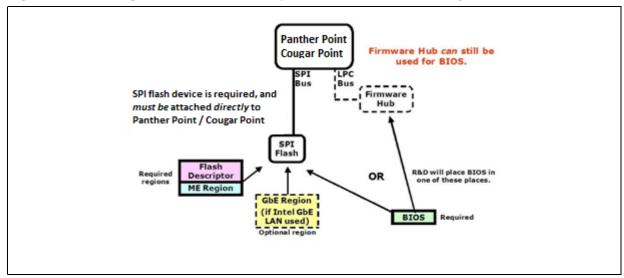

| A-3          | Configuration "C" — Desktop/Server/Workstation Only 60                                 |  |  |  |  |

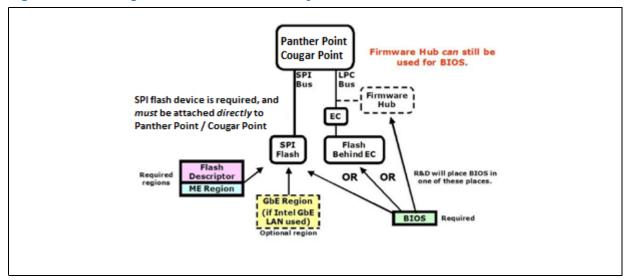

| A-4          | Configuration "D" — Mobile Only 60                                                     |  |  |  |  |

| B-1          | Intel® 7 Series/C216 Chipset Family Full Clock Integration Mode Architecture 61        |  |  |  |  |

| 1-1          | Number Format Notation                                                                 |  |  |  |  |

| 1-2          | Data Format Notation                                                                   |  |  |  |  |

| 1-3          | Kit Contents                                                                           |  |  |  |  |

| 2-1          | Flash Image   PDR Region                                                               |  |  |  |  |

| 2-2          | Flash Image   GbE Region                                                               |  |  |  |  |

| 2-3          | Flash Image   ME Region                                                                |  |  |  |  |

| 2-4          | Flash Image   BIOS Region                                                              |  |  |  |  |

| 2-5          | Flash Image   Descriptor Region                                                        |  |  |  |  |

| 2-6          | Flash Image   Descriptor Region   Descriptor Map                                       |  |  |  |  |

| 2-7          | Flash Image   Descriptor Region   Component Section                                    |  |  |  |  |

| 2-8          | Flash Image   Descriptor Region   Master Access Section   CPU/BIOS                     |  |  |  |  |

| 2-9          | Flash Image   Descriptor Region   Master Access Section   Manageability Engine (ME) 26 |  |  |  |  |

| 2-10         | Flash Image   Descriptor Region   Master Access Section   GbE LAN                      |  |  |  |  |

| 2-11         | Flash Image   Descriptor Region   VSCC Table   Add Table Entry                         |  |  |  |  |

| 2-12         | Flash Image   Descriptor Region   VSCC Table   W25Q64BV (example)                      |  |  |  |  |

| 2-13         | Flash Image   Descriptor Region   OEM Section                                          |  |  |  |  |

| 2-14         | Flash Image   Descriptor Region   PCH Straps   PCH Strap 0                             |  |  |  |  |

| 2-15         | Flash Image   Descriptor Region   PCH Straps   PCH Strap 2                             |  |  |  |  |

| 2-16         | Flash Image   Descriptor Region   PCH Straps   PCH Strap 4                             |  |  |  |  |

| 2-17         | Flash Image   Descriptor Region   PCH Straps   PCH Strap 7                             |  |  |  |  |

| 2-18         | Flash Image   Descriptor Region   PCH Straps   PCH Strap 9                             |  |  |  |  |

| 2-19         | Flash Image   Descriptor Region   PCH Straps   PCH Strap 10                            |  |  |  |  |

| 2-20         | Flash Image   Descriptor Region   PCH Straps   PCH Strap 15                            |  |  |  |  |

| 2-21         | Flash Image   Descriptor Region   PCH Straps   PCH Strap 15                            |  |  |  |  |

| 2-22<br>2-23 | Flash Image   Descriptor Region   PCH Straps   PCH Strap 16                            |  |  |  |  |

| 2-23<br>2-24 | Flash Image   Descriptor Region   PCH Straps   PCH Strap 17                            |  |  |  |  |

| Z-Z4         | Tiasi image   ME Negion   Comiguration   ME                                            |  |  |  |  |

| 2-25         | Flash Image   ME Region   Configuration   Power Packages                              |  |  |

|--------------|---------------------------------------------------------------------------------------|--|--|

| 2-25         | Flash Image   ME Region   Configuration   Features Supported                          |  |  |

| 2-20<br>2-27 | Flash Image   ME Region   Configuration   Intel® Anti-Theft Technology                |  |  |

| 2-27         | Flash Image   ME Region   Configuration   ME Debug Event Service                      |  |  |

| 2-26<br>2-29 | 42                                                                                    |  |  |

| 2-29         | Flash Image   ME Region   Configuration   ICC Data   ICC Profile 0   FCIM/BTM Spe-    |  |  |

| 2-30         | cific Registers                                                                       |  |  |

| 2-31         | Flash Image   ME Region   Configuration   ICC Data   ICC Profile 0   ICC Registers .  |  |  |

|              | 45                                                                                    |  |  |

| 2-32         | Flash Image   ME Region   Configuration   ICC Data   ICC Profile 0   Clock Range Def- |  |  |

|              | inition Record 0                                                                      |  |  |

| 3-1          | Common Bring Up Issues and Troubleshooting Table 57                                   |  |  |

| B-1          | SSC Blocks                                                                            |  |  |

| B-2          | Clock Dividers                                                                        |  |  |

| B-3          | Clock Source Select Parameters                                                        |  |  |

| B-4          | SRC Source Select Parameters                                                          |  |  |

| B-5          | Flex Clock Source Select Parameters                                                   |  |  |

| B-6          | PLL Reference Clock Select Parameters                                                 |  |  |

| B-7          | PLL Enable Parameters                                                                 |  |  |

| B-8          | Output Clock Enable Parameters                                                        |  |  |

| B-9          | ·                                                                                     |  |  |

| B-10         | Divider Enable Parameters                                                             |  |  |

| B-11         | Power Management Parameters74                                                         |  |  |

| B-12         | Power Management Parameters 75                                                        |  |  |

| B-13         |                                                                                       |  |  |

| B-14         |                                                                                       |  |  |

| B-15         |                                                                                       |  |  |

| B-16         | 5                                                                                     |  |  |

| B-17         | 3                                                                                     |  |  |

| B-18         | Phase Interpolators 1 & 2 Biasing Parameters                                          |  |  |

| B-19         |                                                                                       |  |  |

| B-20         | D PCH Clock output / ICC registers mapping - part A84                                 |  |  |

| B-21         | PCH Clock output / ICC registers mapping - part B                                     |  |  |

# **Revision History**

| Revision   | Description                                                | Date       |

|------------|------------------------------------------------------------|------------|

| 8.1.0.1237 | Beta Release: See change bars on the left side of the page | March 2012 |

| 8.1.0.1248 | PC Release: See change bars on the left side of the page   | June 2012  |

| 8.1.0.1248 | PV Release: See change bars on the left side of the page   | July 2012  |

§ §

## 1 Introduction

This document covers the Intel $^{\circledR}$  Management Engine Firmware (Intel $^{\circledR}$  ME) 8.1 - 1.5MB SKU Firmware bring up procedure. Intel $^{\circledR}$  ME is tied to essential platform functionality — this dependency cannot be avoided for engineering reasons.

The bring up procedure primarily involves building a Serial Peripheral Interface (SPI) Flash image that will contain:

- **[required]** Descriptor region Contains sizing information for all other SPI Flash image regions, SPI settings (including Vendor Specific Configuration or VSCC tables, SPI device parameters), and region access permissions.

- [required] BIOS region Contains firmware for the processor (or host) and/or Embedded Controller (EC).

- **[required]** Intel<sup>®</sup> ME FW region Contains firmware for the Intel<sup>®</sup> Management Engine.

- **[optional]** GbE region Contains firmware for Intel<sup>®</sup> LAN solution.

For more details on SPI Flash layout, see the document *Intel®* 7 *Series/C216 Chipset Family SPI Flash Programming Guide* and Appendix A. Once the SPI Flash image is built, it will be programmed to the target Intel® 7 Series/C216 Chipset Family based platform and the platform will be booted. This document also covers any tests and checks required to ensure that this boot process is successful and that Intel® ME 1.5MB FW is operating as expected.

#### 1.1 Related Documentation

VIP: Kit# 474804 - Intel® Ethernet Network Connections (16.3 PC OEM Gen) - LAN Software Drivers -- 05-May-2011 LAN Acess Division (LAD) - V16.3C00061 TIC = 239717 .Release 16.3 Production Candidate with selected bug fixes for E1K, E1C and IXE silicon products.

## 1.2 Intel® ME FW Features

This firmware release includes the following applications:

- Platform Clocks Tune Intel<sup>®</sup> 7 Series/C216 Chipset Family clock silicon to the parameters of a specific board, configure clocks at run time, and power management clocks. **Benefit:** Allows extensive customizability and soft control of "Third generation" clock solution and makes clocks available before CPU powers up.

- Silicon Workaround Capability Intel<sup>®</sup> ME FW will have limited capabilities to perform targeted workarounds for silicon issues. **Benefit:** Allows Intel<sup>®</sup> ME FW to address some issues that otherwise would require a new silicon stepping.

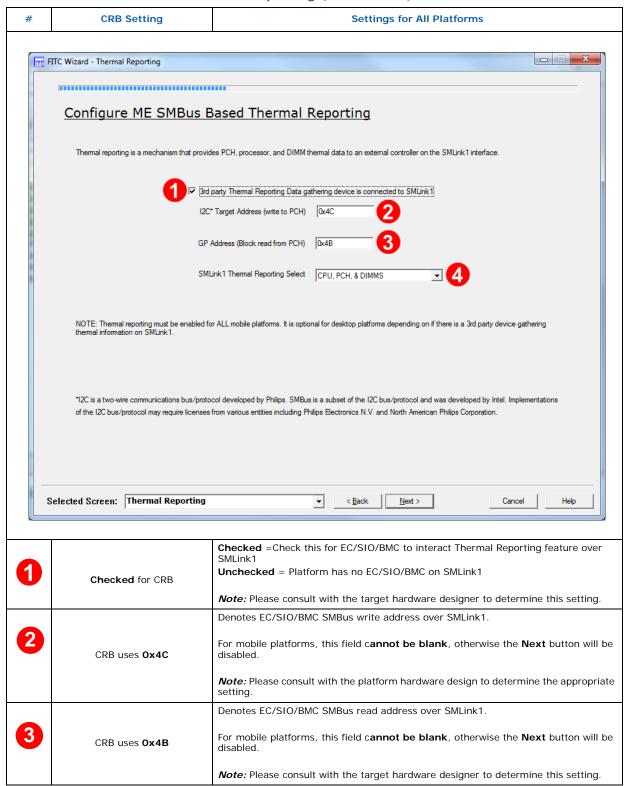

- Thermal Reporting Intel<sup>®</sup> ME FW has the ability to collect platform thermal data and provide that data to embedded controllers and super I/O devices over SMLINK1 as well as in memory map I/O space.

## 1.3 Prerequisites

Before this document is read and utilized, it is essential that the reader first review the 1.5MB FW Release Notes (included with this Intel<sup>®</sup> ME 1.5MB FW kit).

This document is constructed so that the reader can complete the bring up steps as given for the Intel Customer Reference Board (CRB). However, in the case that bring up is being performed on a different Intel<sup>®</sup> 7 Series Family based platform, this document will highlight any changes that must be imposed onto the bring up steps accordingly.

This document makes only the following limited assumptions regarding hardware:

- The platform is Intel® 7 Series Family based

- The platform is equipped with one or more SPI Flash devices with a total capacity sufficient for storing all relevant firmware images.

## 1.4 Acronyms and Definitions

#### 1.4.1 General

| Acronym or Term        | Definition                                                                 |

|------------------------|----------------------------------------------------------------------------|

| API                    | Application Programming Interface                                          |

| ASCII                  | American Standard Code for Information Interchange                         |

| BIOS                   | Basic Input Output System                                                  |

| CPU                    | Central Processing Unit                                                    |

| DIMM                   | Dual In-line Memory Module                                                 |

| DLL                    | Dynamic Link Library                                                       |

| DMI                    | Direct Media Interface                                                     |

| EC                     | Embedded Controller                                                        |

| EEPROM                 | Electrically Erasable Programmable Read Only Memory                        |

| FDI                    | Flexible Display Interface                                                 |

| FW                     | Firmware                                                                   |

| GbE                    | Gigabit Ethernet                                                           |

| HECI                   | Host Embedded Controller Interface (aka Intel <sup>®</sup> MEI)            |

| IBV                    | Independent BIOS Vendor                                                    |

| ID                     | Identification                                                             |

| Intel® ME              | Intel® Management Engine (Intel®ME)                                        |

| Intel <sup>®</sup> MEI | Intel® Management Engine Interface (Intel® MEI) (renamed from HECI)        |

| Intel® IPT             | Intel <sup>®</sup> Identity Protection Technology (Intel <sup>®</sup> IPT) |

| IMSS                   | Intel® Management and Security Status Application                          |

| ISV                    | Independent Software Vendor                                                |

| JTAG                   | Joint Test Action Group                                                    |

| KVM                    | Keyboard, Video, Mouse                                                     |

| LAN                    | Local Area Network                                                         |

| LED                    | Light Emitting Diode                                                       |

| NVM                    | Non-Volatile Memory                                                        |

| Acronym or Term | Definition                                        |  |

|-----------------|---------------------------------------------------|--|

| NVRAM           | Non-Volatile Random Access Memory                 |  |

| ООВ             | Out-of-Band                                       |  |

| OS              | Operating System                                  |  |

| PAVP            | Protected Audio and Video Path                    |  |

| PCI             | Peripheral Component Interconnect                 |  |

| PCIe*           | Peripheral Component Interconnect Express         |  |

| PHY             | Physical Layer (Networking)                       |  |

| PRTC            | Protected Real Time Clock                         |  |

| RNG             | Random Number Generator                           |  |

| RSA             | RSA is a public key encryption method             |  |

| RTC             | Real Time Clock                                   |  |

| SDK             | Software Development Kit                          |  |

| SHA             | Secure Hash Algorithm                             |  |

| SMBus           | System Management Bus                             |  |

| SPI Flash       | Serial Peripheral Interface Flash                 |  |

| TCP/IP          | Transmission Control Protocol / Internet Protocol |  |

| TPM             | Trusted Platform Module                           |  |

| UI              | User Interface                                    |  |

| UNS             | User Notification Service                         |  |

| VSCC            | Vendor Specific Configuration                     |  |

| WMI             | Windows Management Instrumentation                |  |

## 1.4.2 Intel<sup>®</sup> Management Engine

| Acronym or Term                                                            | Definition                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3PDS                                                                       | 3rd Party Data Storage                                                                                                                                                                                                                                  |

| Agent                                                                      | Software that runs on a client PC with OS running                                                                                                                                                                                                       |

| Intel <sup>®</sup> AT                                                      | Intel <sup>®</sup> Anti-Theft Technology (Intel <sup>®</sup> AT)                                                                                                                                                                                        |

| End User                                                                   | The person who uses the computer (either Desktop or Mobile). In corporate, the user usually does not have an administrator privileges.                                                                                                                  |

| Host or Host CPU                                                           | The processor that is running the operating system. This is different than the management processor running the Intel® Management Engine Firmware.                                                                                                      |

| Host Service/Application                                                   | An application that is running on the host CPU                                                                                                                                                                                                          |

| INF                                                                        | An information file (.inf) used by Microsoft* operating systems that supports the Plug & Play feature. When installing a driver, this file provides the OS the necessary information about driver filenames, driver components, and supported hardware. |

| Intel <sup>®</sup> Management Engine<br>Interface (Intel <sup>®</sup> MEI) | Interface between the Management Engine and the Host system                                                                                                                                                                                             |

| Intel <sup>®</sup> MEI driver                                              | Intel $^{\rm @}$ ME host driver that runs on the host and interfaces between ISV Agents and the Intel $^{\rm @}$ ME HW.                                                                                                                                 |

| IT User                                                                    | Information Technology User. Typically very technical and uses a management console to ensure multiple PCs on a network function.                                                                                                                       |

| Acronym or Term   | Definition                                                                                                                                                                                         |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LMS               | Local Management Service: A SW application which runs on the host machine and provide a secured communication between the ISV agent and the Intel® Management Engine Firmware.                     |

| Intel® ME         | Intel® Management Engine: The embedded processor residing in the chipset PCH                                                                                                                       |

| MECI              | ME-VE Communication Interface                                                                                                                                                                      |

| NVM               | Non-Volatile Memory: A type of memory that will retain its contents even if power is removed.                                                                                                      |

| OOB Interface     | Out Of Band interface: This is SOAP/XML interface over secure or non-secure TCP protocol.                                                                                                          |

| OS not Functional | The Host OS is considered non-functional in Sx power state and any one of the following cases when system is in S0 power state:  OS is hung After PCI reset OS watch dog expires OS is not present |

| System States     | Operating System power states such as S0. See detailed definitions in System States and Power Management section.                                                                                  |

| UIM               | User Identifiable Mark                                                                                                                                                                             |

## 1.4.3 System States and Power Management

| Acronym or Term | Definition                                                                                                                                                                                                                                                                                                                   |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G3              | A system state of Mechanical Off where all power is disconnected from the system. G3 power state does not necessarily indicate that RTC power is removed.                                                                                                                                                                    |

| MO              | Intel <sup>®</sup> Management Engine power state where all HW power planes are activated. The host power state is S0.                                                                                                                                                                                                        |

| МЗ              | Intel <sup>®</sup> Management Engine power state where all HW power planes are activated however the host power state is different than S0 (Some host power planes are not activated). Host PCIe* interface are unavailable to the host software. Main memory is not available for Intel <sup>®</sup> Management Engine use. |

| M-Off           | No power is applied to the management processor subsystem. Intel® Management Engine is not operating.                                                                                                                                                                                                                        |

| OS Hibernate    | System state where the OS state is saved on the hard drive.                                                                                                                                                                                                                                                                  |

| S0              | A system state where power is applied to all HW devices and the system is running normally.                                                                                                                                                                                                                                  |

| S1, S2, S3      | A system state where the host CPU is halted but power remains available to the memory system (memory is in self-refresh mode).                                                                                                                                                                                               |

| S4              | A system state where the host CPU and memory are not active.                                                                                                                                                                                                                                                                 |

| S5              | A system state where all power to the host system is off, however the power cord (and/or battery in mobile designs) is still connected.                                                                                                                                                                                      |

| Shut Down       | Equivalent to the S5 state.                                                                                                                                                                                                                                                                                                  |

| Snooze Mode     | Intel® Management Engine activities are mostly suspended to save power. The Intel® Management Engine monitors HW activities and can restore its activities depending on the HW event.                                                                                                                                        |

| Standby         | System state where the OS state is saved in memory and resumed from the memory when mouse/keyboard is clicked.                                                                                                                                                                                                               |

| Sx              | All S states which are different than S0.                                                                                                                                                                                                                                                                                    |

### 1.5 Reference Documents

| Document                                                                                                                                                                         | Doc Number/<br>Location* |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Maho Bay and Carlow-WS – Platform Design Guide                                                                                                                                   | 473718 / IBL             |

| Chief River Mobile CRB– Platform Design Guide                                                                                                                                    | 29635 / IBL              |

| Intel <sup>®</sup> Management Engine (Intel <sup>®</sup> ME) and Embedded Controller Interaction for Chief River Platform                                                        | 471984 / IBL             |

| RS – Intel <sup>®</sup> Management Engine BIOS Writers Guide                                                                                                                     | 31007 / *                |

| [Maho Bay / Chief River / Carlow] Platforms - Intel® Management Engine (Intel® ME) 8.0 - 1.5 MB SKU Firmware for Intel® 7 Series Family - Compliancy and Testing Guide -Rev. 0.8 | 464265 / IBL             |

| Intel <sup>®</sup> 82576 and 82579 Gigabit Ethernet Controllers – Intel Software Support for Cisco's MACsec Protocol Supplicant – 10-Dec-2010                                    | 461067 / IBL             |

**Note:** \* Unless specified otherwise, a document can be ordered by providing its reference number to your Intel Field Applications Engineer.

#### 1.6 Format and Notation

The formats and notations used within this document model are those typically used by BIOS vendors. This section describes the formatting and the notations that will be followed in this document.

#### **Table 1-1. Number Format Notation**

| Number Format     | Notation | Example                                                                            |

|-------------------|----------|------------------------------------------------------------------------------------|

| Decimal (default) | d        | 14d. Note that any number without an explicit suffix can be assumed to be decimal. |

| Binary            | b        | 1110b                                                                              |

| Hex               | h        | 0Eh                                                                                |

| Hex               | 0x       | 0x0E                                                                               |

#### Table 1-2. Data Format Notation

| Data Type   | Notation | Size                       |  |

|-------------|----------|----------------------------|--|

| Bit         | b        | Smallest unit, 0 or 1      |  |

| Byte        | В        | 8 bits                     |  |

| Word        | W        | 16 bits or 2 bytes         |  |

| Double-word | DW       | 32 bits or 4 bytes         |  |

| Quad-word   | QW       | 8 bytes or 4 words         |  |

| Kilobyte    | КВ       | 1024 bytes                 |  |

| Megabit     | Mb       | 1,048,576 bits or 128 KB   |  |

| Megabyte    | MB       | 1,048,576 bytes or 1024 KB |  |

| Gigabit     | Gb       | 1,073,741,824 bits         |  |

| Gigabyte    | GB       | 1024 MB                    |  |

## 1.7 Kit Contents

The Intel<sup>®</sup> ME 1.5MB FW kit can be downloaded from VIP (https://platformsw.intel.com/). The contents of this kit are detailed below (Note that only key files are listed).

Table 1-3. Kit Contents (Sheet 1 of 4)

| File or [Directory]                             | Content Description                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [root]                                          | Root directory                                                                                                                                                                                                                                                                                                                                             |

| 1.5MB FW Bring Up Guide.pdf                     | This document                                                                                                                                                                                                                                                                                                                                              |

| 1.5MB FW Getting Started Guide.pdf              | 1.5MB FW Getting started guide.                                                                                                                                                                                                                                                                                                                            |

| SPI programming guide.pdf                       | How to program SPI device parameters, VSCC tables, descriptor region details. Also contains a complete SPI Flash softstrap reference.                                                                                                                                                                                                                      |

| [Image Components]                              |                                                                                                                                                                                                                                                                                                                                                            |

| [BIOS]                                          |                                                                                                                                                                                                                                                                                                                                                            |

| IVB091.rom                                      | BIOS image only for Intel® CRB. This BIOS image works for both desktop and mobile CRBs.  For other Intel® 7 Series Family based platforms, a custom BIOS image will be required.                                                                                                                                                                           |

| [GbE]                                           |                                                                                                                                                                                                                                                                                                                                                            |

| 82579_NVM_4_DESKTOP.bin                         | Intel <sup>®</sup> LAN PHY firmware image, supports <b>PHY A2</b> and <b>BO only</b> . This image is recommended for testing power flows with connectivity. This image is for desktop platforms only.                                                                                                                                                      |

| 82579_NVM_3_MOBILE.bin                          | Intel <sup>®</sup> LAN PHY firmware image, supports <b>PHY A2</b> and <b>BO only</b> . This image is recommended for testing power flows with connectivity. This image is for mobile platforms only.                                                                                                                                                       |

| [ME]                                            |                                                                                                                                                                                                                                                                                                                                                            |

| ME8_1.5M_PreProduction.BIN                      | Intel® ME firmware image (Non Production FW) - supports unfused Intel® 7 Series Family PCH steppings: • Unfused PPT ESO (B0 Super SKU)  Note: For PAVP Testing, you must match Production FW with Production Part and Non Production FW with Non Production Parts.                                                                                         |

| ME8_1.5M_Production.BIN                         | Intel <sup>®</sup> ME firmware image ( <b>Production FW</b> ) - supports <b>fused</b> and <b>unfused</b> Intel <sup>®</sup> 7 Series Family PCH steppings:  • Unfused PPT ESO (B0 Super SKU)  • Fused PPT Pre-QS and QS <b>Note: For PAVP Testing</b> , you must match Production FW with Production Part and Non Production FW with Non Production Parts. |

| [Installers]                                    |                                                                                                                                                                                                                                                                                                                                                            |

| Intel <sup>®</sup> ME SW Installation Guide.pdf | Intel®ME SW Installation Guide                                                                                                                                                                                                                                                                                                                             |

| [ME_SW]                                         |                                                                                                                                                                                                                                                                                                                                                            |

| Setup.exe                                       | Install executable (non-InstallShield) of Intel <sup>®</sup> ME Drivers for Windows* OS. See readme.txt for more information.                                                                                                                                                                                                                              |

| [ME_SW_IS]                                      |                                                                                                                                                                                                                                                                                                                                                            |

Table 1-3. Kit Contents (Sheet 2 of 4)

| File or [Directory]                                                      | Content Description                                                                                                                              |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| ME_SW_IS.zip                                                             | Zip containing InstallShield* files of Intel <sup>®</sup> ME Drivers for Windows* OS. See readme.txt in previous directory for more information. |

| [Tools]                                                                  |                                                                                                                                                  |

| [ICC_Tools]                                                              |                                                                                                                                                  |

| Intel(R) ME Firmware Integrated Clock Control (ICC) Tools User Guide.pdf | ICC Tools User Guide                                                                                                                             |

| [ССТ]                                                                    |                                                                                                                                                  |

| DOS                                                                      |                                                                                                                                                  |

| cct.exe                                                                  | Clock Control Tool (CCT)                                                                                                                         |

| EFI                                                                      |                                                                                                                                                  |

| cct.efi                                                                  | CCT for EFI                                                                                                                                      |

| Windows                                                                  |                                                                                                                                                  |

| cct.ini                                                                  | Configuration file for CCT                                                                                                                       |

| cctWin.exe                                                               | CCT for Windows*                                                                                                                                 |

| [System Tools]                                                           |                                                                                                                                                  |

| Open Watcom Public License.pdf                                           | Sybase Open Watcom Public License version 1.0 document.                                                                                          |

| System Tools User Guide.pdf                                              | System Tools User Guide                                                                                                                          |

| Tools_Version.txt                                                        | Tools version information                                                                                                                        |

| [Flash Image Tool]                                                       |                                                                                                                                                  |

| fitc.exe                                                                 | Flash Image Tool (FITC & FITC Wizard)                                                                                                            |

| fitc.ini                                                                 | Configuration file for FITC & FITC Wizard                                                                                                        |

| fitctmpl.xml                                                             | FITC Tool XML file                                                                                                                               |

| newfiletmpl.xml                                                          | FITC Configuration XML file                                                                                                                      |

| fitcwizardhelp.chm                                                       | Wizard Help text file                                                                                                                            |

| vsccommn.bin                                                             | Binary containing the supported SPI parts                                                                                                        |

| VSCCommn_bin Content.pdf                                                 | Documentation listing the SPI parts supported by vscccommn.bin                                                                                   |

| [Flash Programming Tool]                                                 |                                                                                                                                                  |

| [DOS]                                                                    |                                                                                                                                                  |

| fparts.txt                                                               | List of supported SPI Flash devices with specific Flash parameters                                                                               |

| fpt.exe                                                                  | Flash Programming Tool (FPT) for DOS                                                                                                             |

| [EFI]                                                                    |                                                                                                                                                  |

| fparts.txt                                                               | List of supported SPI Flash devices with specific Flash parameters                                                                               |

| fpt.efi                                                                  | Flash Programming Tool (FPT) for EFI                                                                                                             |

| [Windows]                                                                |                                                                                                                                                  |

| fparts.txt                                                               | List of supported SPI Flash devices with specific Flash parameters                                                                               |

| fptw.exe                                                                 | Flash Programming Tool (FPT) for Windows*                                                                                                        |

| [Windows64]                                                              |                                                                                                                                                  |

Table 1-3. Kit Contents (Sheet 3 of 4)

| File or [Directory]      | Content Description                                                |

|--------------------------|--------------------------------------------------------------------|

| fparts.txt               | List of supported SPI Flash devices with specific Flash parameters |

| fptw64.exe               | Flash Programming Tool (FPT) for Windows* (64-bit) OS              |

| [FWUpdate]               |                                                                    |

| [EFI]                    |                                                                    |

| FWUpdLcl.efi             | FW Update Tool (EFI version)                                       |

| [Local-DOS]              |                                                                    |

| FWUpdLcl.exe             | FW Update Tool (DOS version)                                       |

| [Local-Win]              |                                                                    |

| FWUpdLcl.exe             | FW Update Tool (Windows* version 32bit)                            |

| [Local-Win64]            |                                                                    |

| FWUpdLcI64.exe           | FW Update Tool (Windows* version 64bit)                            |

| [MEInfo]                 |                                                                    |

| [DOS]                    |                                                                    |

| MEInfo.exe               | Intel®ME Information Tool (DOS version)                            |

| [EFI]                    |                                                                    |

| MEInfo.efi               | Intel®ME Information Tool (EFI version)                            |

| [Windows]                |                                                                    |

| MEI nfoWin.exe           | Intel®ME Information Tool (Windows* version 32bit)                 |

| [Windows64]              |                                                                    |

| MEInfoWin64.exe          | Intel®ME Information Tool (Windows* version 64bit)                 |

| [MEManuf]                |                                                                    |

| [DOS]                    |                                                                    |

| MEManuf.cfg              | Intel®ME Manufacturing Tool config file                            |

| MEManuf.exe              | Intel®ME Manufacturing Tool (DOS version)                          |

| vsccommn.bin             | Binary containing the supported SPI parts                          |

| VSCCommn_bin Content.pdf | Documentation listing the SPI parts supported by vscccommn.bin     |

| [EFI]                    |                                                                    |

| MEManuf.cfg              | Intel®ME Manufacturing Tool config file                            |

| MEManuf.efi              | Intel®ME Manufacturing Tool (EFI version)                          |

| vsccommn.bin             | Binary containing the supported SPI parts                          |

| [Windows]                |                                                                    |

| MEManuf.cfg              | Intel®ME Manufacturing Tool config file                            |

| MEManufWin.exe           | Intel <sup>®</sup> ME Manufacturing Tool (Windows* version 32bit)  |

| vsccommn.bin             | Binary containing the supported SPI parts                          |

| VSCCommn_bin Content.pdf | Documentation listing the SPI parts supported by vscccommn.bin     |

| [Windows64]              |                                                                    |

### Table 1-3. Kit Contents (Sheet 4 of 4)

| File or [Directory] |              | Content Description                                               |  |

|---------------------|--------------|-------------------------------------------------------------------|--|

|                     | MEManuf.cfg  | Intel®ME Manufacturing Tool config file                           |  |

| MEManufWin64.exe    |              | Intel <sup>®</sup> ME Manufacturing Tool (Windows* version 64bit) |  |

|                     | vsccommn.bin | Binary containing the supported SPI parts                         |  |

## 1.8 External Hardware Requirements for Bring Up

Acquire the following hardware tools before moving on to the next step.

| Windows* OS System                                                                                                                         | Flash Burner                                                                                                                                                                                                                                                                              | DOS Bootable USB Key                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                            |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                         |

| Equipment:  • Laptop or desktop that supports win32 applications  Purpose:  • Will run firmware image assembly and build process software. | Equipment:  • (Optional) For platforms that don't boot, a Flash Chip Programmer will be required  • For platforms that can boot to DOS or Windows*, a Flash Programming Tool (FPT) is provided in this kit  Purpose:  • Will burn firmware images onto the target system Flash device(s). | Equipment:  • A DOS Bootable USB Key (Size > 512 MB)  Purpose:  • Acting as a bootable device and will be used to run Flash Programming Tool (fpt.exe) directly on the system that is undergoing Bring Up process.  • Or will be used to transfer a firmware image onto a Flash burner. |

# 2 Image Creation: Flash Image Tool (FITC)

Flash Image Tool (FITC) will be used to generate a full SPI Flash binary image with Descriptor, GbE, BIOS, and Intel<sup>®</sup> ME Regions. Use the steps shown in following sections.

**Note:** The FITC Tool may be updated throughout the release cycles. As a general rule, please ensure you use the tools, images and other content from the same kit and refrain from using different version tools.

After this SPI Flash image is created, it will need to be burned onto the target platform's SPI Flash device(s). Section 3, "Programming SPI Flash Devices and Checking Firmware Status" later in this document provides steps to do this.

### 2.1 Start FITC and Set Up The Build Environment

- Invoke Flash Image Tool. Using Explorer\*, navigate to [root]\Tools\System

Tools\Flash Image Tool. Ensure that FITC's directory contents are intact (see

Section 1.7). Double-click fitc.exe.

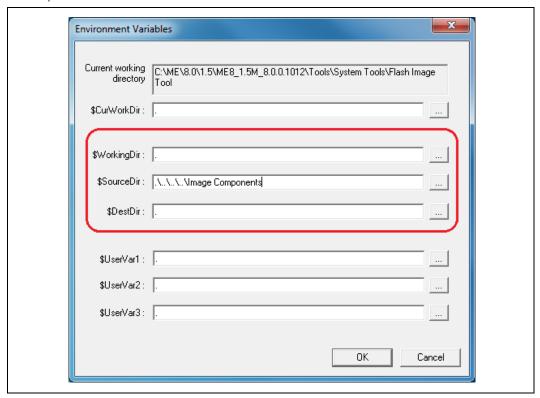

- 2. In the main menu select **Build | Environment Variables...**. Edit your configuration as shown below. Note that in the example, **[root]\Tools\System Tools\Flash I mage Tool** is ".".

- Keep the Working Directory \$WorkingDir as "."

- Source Directory \$SourceDir is where FITC will look to find binary images during the image creation process, change \$SourceDir to ".\..\..\Image Components"

- Destination Directory \$DestDir is where FITC will save the SPI Flash binary image, keep \$DestDir as "."

Figure 2-1. Build | Environment Variables

3. Click **OK** to apply your changes.

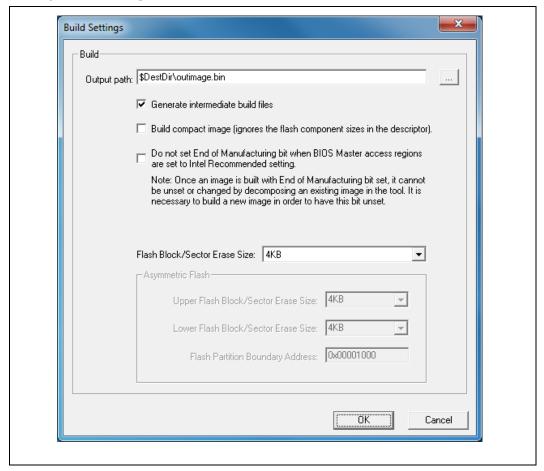

4. In the main menu select **Build | Build Settings...**. Leave the defaults for **Output path**, **Generate intermediate build files**, **and Build compact image** as shown. Change the **Flash Block/Sector Erase Size** as appropriate for your SPI flash part(s). Click **OK** to apply your changes.

Figure 2-2. Build | Build Settings...

5. In the main menu select **File | Open...**. In the Open dialog that appears navigate to **[root]\Tools\System Tools\Flash I mage Tool**. Click on **newfiletmpl.xml** and click **OK**.

## 2.2 Configure PCH Silicon Stepping

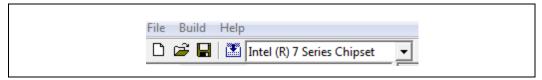

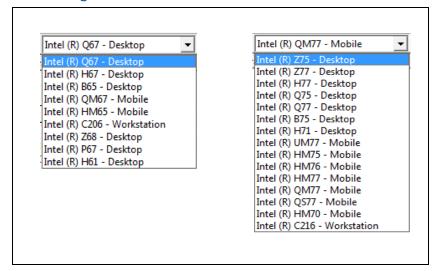

Leave the PCH Silicon Stepping Combo Box at its default value of  $Intel^{\circledR}$  7 Series Chipset.

Figure 2-3. PCH Silicon Stepping Combo Box

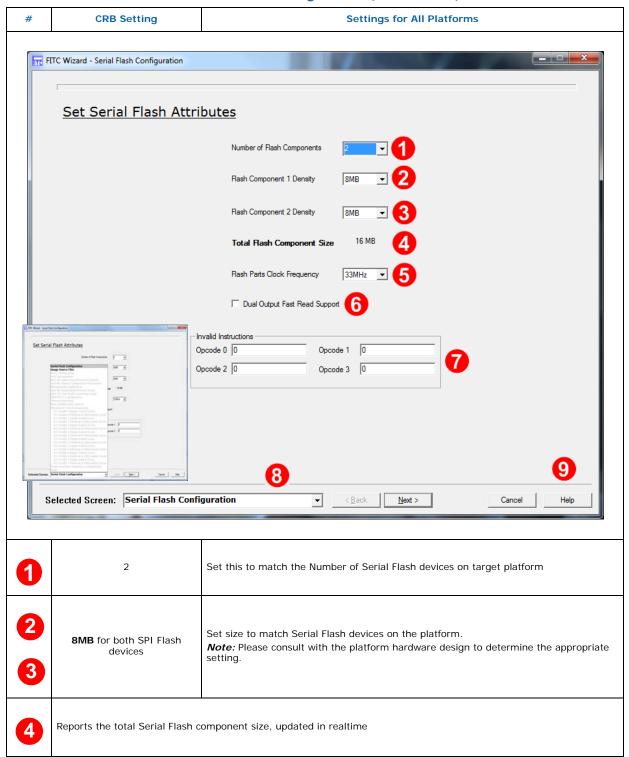

## 2.3 Set Up SPI Flash Regions

Table 2-1. Flash Image | PDR Region

| Location                                                                                                                                                                        | Parameter         | CRB Set To               | Settings for Any Platform                                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|------------------------------------------------------------------------------|--|

| Follow navigation tree below:  • Select the Flash Image                                                                                                                         | PDR Region Length | PDR Region is enabled    | Displays Region size information when <b>Binary input file</b> is specified. |  |

| Select Flash Image   PDR Region     Set the parameters in the PDR Region section as shown                                                                                       | Binary Input File | PDR Region is<br>enabled | Load a Platform Data Region binary if required and available.                |  |

| Flash Image  Descriptor Region  Descriptor Map  Component Section  Master Access Section  PCH Straps  Upper Map  VSCC Table  OEM Section  PDR Region  ME Region  ME Region      |                   |                          |                                                                              |  |

| or if NOT using Platform Data Region (PDR)                                                                                                                                      |                   |                          |                                                                              |  |

| A red "X" will indicate whether this Region is disabled. If this Region is not disabled, disable it by right-clicking on Flash Image   PDR Region and selecting Disable Region. |                   |                          | VSCC Table OEM Section PDR Region GbE Region                                 |  |

Table 2-2. Flash I mage | GbE Region

| Location                                                                                                                                                                         | Parameter                                     | CRB Set To                                                                                                                                                                                                                                                        | Settings for Any Platform                                                                                                                                                                                  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Follow navigation tree below:  • Select the Flash Image                                                                                                                          | Yellow means custom settings may be required. |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                            |  |

| Select the Hash Image   GbE Region                                                                                                                                               | GbE LAN region length                         | 0x00000000                                                                                                                                                                                                                                                        |                                                                                                                                                                                                            |  |

| Set the parameters in the GbE Region section as shown  Flash Image  Flow Descriptor Region  DR Region  GbE Region                                                                | Binary input file                             | Navigate to your <b>Source Directory</b> (as specified in Section 2.1) and switch to the <b>GbE</b> subdirectory.  Choose the appropriate Intel <sup>®</sup> GbE LAN Firmware binary image.  If not using Intel <sup>®</sup> LAN then leave this parameter blank. |                                                                                                                                                                                                            |  |

| ME Region BIOS Region                                                                                                                                                            | Intel <sup>®</sup> Integrated<br>LAN Enable   | true                                                                                                                                                                                                                                                              | This field only is editable after an Intel <sup>®</sup> integrated LAN image is loaded. If not planning to validate Intel <sup>®</sup> LAN on target platform, or for debug reasons, set to <b>false</b> . |  |

|                                                                                                                                                                                  | Major Version                                 | 0                                                                                                                                                                                                                                                                 | Displays major revision value for Intel <sup>®</sup> LAN GbE FW version when <b>Binary input file</b> is specified.                                                                                        |  |

|                                                                                                                                                                                  | Minor Version                                 | 0                                                                                                                                                                                                                                                                 | Displays minor revision value for Intel <sup>®</sup> LAN GbE FW version when <b>Binary input file</b> is specified.                                                                                        |  |

|                                                                                                                                                                                  | Image ID                                      | 0                                                                                                                                                                                                                                                                 | Displays image ID value for Intel <sup>®</sup> LAN GbE FW version when <b>Binary input file</b> is specified.                                                                                              |  |

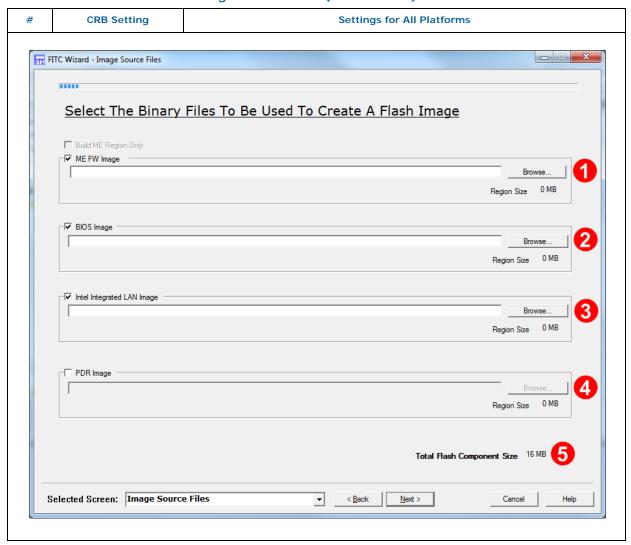

| or if not using Intel <sup>®</sup> wired LAN device                                                                                                                              |                                               |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                            |  |